clock ipotetico

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Ciao.

pensavo di fare una sistesi tra diverse cose molto popolari che ho trovato

i post di DIY sono questi:http://www.diyaudio.com/forums/showthre ... post734144

e

http://www.diyaudio.com/forums/showthre ... post730231

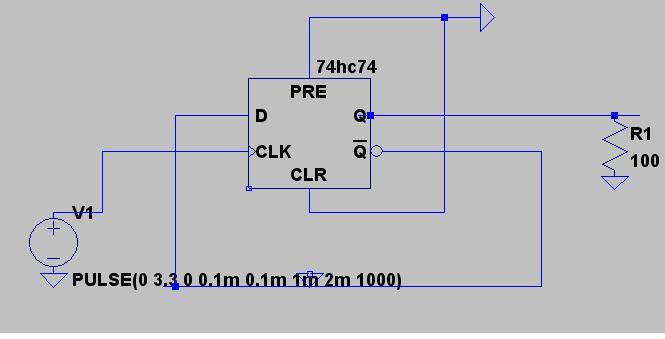

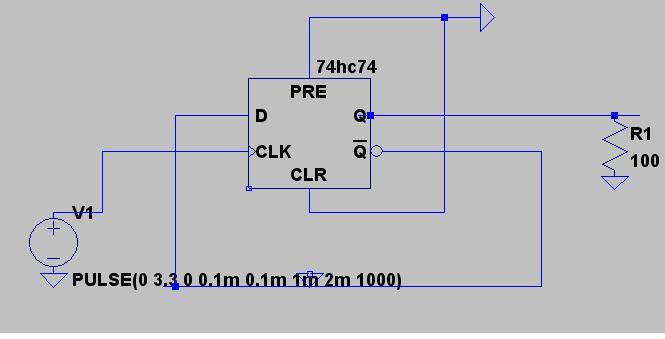

L'IC usato, a valle del clock, per dividere in due la frequenza fornita allo SAA7220p/B dovrebbe essere il philips 74hct74

Pensavo di usare, se riesco a reperirlo, un quarzo della rapid electronic inglese, di tipo DIL8.

Oppure, la prima scelta, l'XO di Guido Tent.. che costa circa 29 euro+6 di shipping (forse qui si potrebbe aprire un discorso su cosa sia un cristallo risonante privo di jitter, e come si misura la differenza fra un quarzo "jitterizzante" e uno no, premesso il corpo DIL 8 e la tolleranza termica 100PPM di entrambi).

Ad ogni buono conto, mentre a valle del clock ci sarebbe l'IC philips, per l'alimentatore avrei pensato a questo:

http://www.tnt-audio.

com/clinica/regulators_noise4_e.html oppure anche la semplicissimo zener della pagina precedente, sempre su TNT. Per ragioni di comodità, potrei prelevare l'alimentazione dal pin IN del regolatore di tensione del +10 V, nel supply del cdp.

Che ne pensate, c'è qualcuno che pensa valga la pena di strutturare questa ideucola, o che ha un parere in merito?

Saluti

R.R.

pensavo di fare una sistesi tra diverse cose molto popolari che ho trovato

i post di DIY sono questi:http://www.diyaudio.com/forums/showthre ... post734144

e

http://www.diyaudio.com/forums/showthre ... post730231

L'IC usato, a valle del clock, per dividere in due la frequenza fornita allo SAA7220p/B dovrebbe essere il philips 74hct74

Pensavo di usare, se riesco a reperirlo, un quarzo della rapid electronic inglese, di tipo DIL8.

Oppure, la prima scelta, l'XO di Guido Tent.. che costa circa 29 euro+6 di shipping (forse qui si potrebbe aprire un discorso su cosa sia un cristallo risonante privo di jitter, e come si misura la differenza fra un quarzo "jitterizzante" e uno no, premesso il corpo DIL 8 e la tolleranza termica 100PPM di entrambi).

Ad ogni buono conto, mentre a valle del clock ci sarebbe l'IC philips, per l'alimentatore avrei pensato a questo:

http://www.tnt-audio.

com/clinica/regulators_noise4_e.html oppure anche la semplicissimo zener della pagina precedente, sempre su TNT. Per ragioni di comodità, potrei prelevare l'alimentazione dal pin IN del regolatore di tensione del +10 V, nel supply del cdp.

Che ne pensate, c'è qualcuno che pensa valga la pena di strutturare questa ideucola, o che ha un parere in merito?

Saluti

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Hai ragione, purtroppo non riesco a caricarla.

Ho aggiornato il messaggio con i link ai post di DIY da cui l'idea.

In pratica, si tratta di completare il clock separato classico, con il chip philips, di modo che, da un lato il clock fornisca la frequenza intera al SAA720, e tramite il chip aggiunto, la F/2 al TDA, in modo da recloccare localmente il TDA1541

In tutto il minestrone, pensavo di congegnare il clock con un XO alimentato a Zener, come su TNT, mentre per le connessioni del

philips 74hct74 verso il TDA cercherò di essere più preciso appena riesco a produrre uno schema.

Grazie

R.R.

Ho aggiornato il messaggio con i link ai post di DIY da cui l'idea.

In pratica, si tratta di completare il clock separato classico, con il chip philips, di modo che, da un lato il clock fornisca la frequenza intera al SAA720, e tramite il chip aggiunto, la F/2 al TDA, in modo da recloccare localmente il TDA1541

In tutto il minestrone, pensavo di congegnare il clock con un XO alimentato a Zener, come su TNT, mentre per le connessioni del

philips 74hct74 verso il TDA cercherò di essere più preciso appena riesco a produrre uno schema.

Grazie

SalutiCiao,

l'immagine non si vede, quindi fatico a capire di che si tratta.

Ciao

Andrea

Originally posted by andypairo - 21/03/2006 : 14:04:08

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Due gocce di gin e un'oliva, e oplà!!.

Piergiorgio, puoi darci un esempio che mi/ci possa aiutare? (a capire cosa sono i circuiti constant fraction e ALS)

R.R.

Piergiorgio, puoi darci un esempio che mi/ci possa aiutare? (a capire cosa sono i circuiti constant fraction e ALS)

SalutiSe vuoi fare un clock a basso Jitter e provare qualcosa di diverso (ma già collaudato da decenni) prova un circuito constant-fraction.

Evita la logica HCT, preferisci comparatori analogici ultrafast o al massimo le famiglie logiche ALS.

_________

Piergiorgio

Originally posted by plovati - 21/03/2006 : 14:35:14

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

-

andypairo

- sostenitore

- Messaggi: 689

- Iscritto il: 03 nov 2005, 23:17

- Località: Italy

Non ho ben capito il tipo di collegamento che vorrsti fare, comunque un metodo di reclocking che secondo me può dare ottimi risultati è il seguente:

http://peufeu.free.fr/audio/extremist_d ... ent_3.html

Utilizza un reclocking locale per il DAC e porta il clock opportunamente bufferizzato alla meccanica.

Per il generatore di clock usa un Tent XO (che è già bello pronto), alimentalo con un alimentatore a basso rumore (tipo il superreg di T.Loesch o uno shunt con il TL431 pilotato da un generatore di corrente) e sei a posto con "poco".

Magari potrebbe essere interessante usare lo stesso clock per generare una frequenza adatta al DEM reclocking in modo da avere un TDA altamente ottimizzato.

PS il "tuo" S1 è partito per la Nuova Zelanda...

Ciao

Andrea

http://peufeu.free.fr/audio/extremist_d ... ent_3.html

Utilizza un reclocking locale per il DAC e porta il clock opportunamente bufferizzato alla meccanica.

Per il generatore di clock usa un Tent XO (che è già bello pronto), alimentalo con un alimentatore a basso rumore (tipo il superreg di T.Loesch o uno shunt con il TL431 pilotato da un generatore di corrente) e sei a posto con "poco".

Magari potrebbe essere interessante usare lo stesso clock per generare una frequenza adatta al DEM reclocking in modo da avere un TDA altamente ottimizzato.

PS il "tuo" S1 è partito per la Nuova Zelanda...

Ciao

Andrea

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

La cosa che volevo provare è semplicemente dare il clock allo SAA e al TDA in maniera spearata tramite l'aggiunta al clock di un solo chip, in grado di dividere per due la frequenza principale, visto che il SAA7220 fornisce al DAC la F dimezzata.

Per l'alimentatore del clock di Tent, (o per un banale cristallo XO commerciale) vorrei usare quello che da TNT risulta essere (e pure nel My Ref) l'alimentatore meno rumoroso in assoluto.

Ti irngrazio per il link, che mi pare cmq molto complesso da implementare.

Considera che non sto parlando di una DAC esterno, ma della modifica di un cdplayer integrato.

Mi fa piacere cmq che dopo la mia rinuncia il S1 suoni in un posto così bello come lanuova Zelanda...

R.R.

Per l'alimentatore del clock di Tent, (o per un banale cristallo XO commerciale) vorrei usare quello che da TNT risulta essere (e pure nel My Ref) l'alimentatore meno rumoroso in assoluto.

Ti irngrazio per il link, che mi pare cmq molto complesso da implementare.

Considera che non sto parlando di una DAC esterno, ma della modifica di un cdplayer integrato.

Mi fa piacere cmq che dopo la mia rinuncia il S1 suoni in un posto così bello come lanuova Zelanda...

SalutiNon ho ben capito il tipo di collegamento che vorrsti fare, comunque un metodo di reclocking che secondo me può dare ottimi risultati è il seguente:

http://peufeu.free.fr/audio/extremist_d ... ent_3.html

Utilizza un reclocking locale per il DAC e porta il clock opportunamente bufferizzato alla meccanica.

Per il generatore di clock usa un Tent XO (che è già bello pronto), alimentalo con un alimentatore a basso rumore (tipo il superreg di T.Loesch o uno shunt con il TL431 pilotato da un generatore di corrente) e sei a posto con "poco".

Magari potrebbe essere interessante usare lo stesso clock per generare una frequenza adatta al DEM reclocking in modo da avere un TDA altamente ottimizzato.

PS il "tuo" S1 è partito per la Nuova Zelanda...

Ciao

Andrea

Originally posted by andypairo - 21/03/2006 : 14:55:36

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

- plovati

- sostenitore

- Messaggi: 8078

- Iscritto il: 05 ott 2005, 20:19

- Località: Italy

- Has thanked: 4 times

- Been thanked: 57 times

La tecnica Constant Fraction è una bellissima metodologia usata in elettronica nucleare per otetnere temporizzazioni a basso Jitter.Piergiorgio, puoi darci un esempio che mi/ci possa aiutare? (a capire cosa sono i circuiti constant fraction e ALS)

Originariamente inviato da riccardo - 21/03/2006 : 14:39:14

In sintesi si tratta di prendere due segnali (di clock, sinusoidali, impulsivi ..) ritardare uno rispetto all'altro di pochi nanosecondi, scalarlo di un fattore fisso (da cui il nome) e mandare i due segnali così ottenuti agli ingressi di un comparatore ultrafast.

L'impulso che si ottiene in uscita jittera molto meno di quello in ingresso perchè il fronte 'jitteroso' sarà confrontato con una sua replica.

Credo sia più o meno quello che fanno qui:

http://www.lessloss.com/jitter.html

che è una tecnica sostanzialmente diversa dalla più comune (e per certi versi performante) tecnologia a PLL:

http://www.analog.com/en/prod/0%2C2877% ... %2C00.html

Per le diverse famiglie logiche vedi:

http://corsiadistanza.polito.it/corsi/p ... m_log2.pdf

_________

Piergiorgio

_________

Piergiorgio

Piergiorgio

-

drews

- new member

- Messaggi: 61

- Iscritto il: 14 nov 2005, 23:56

- Località: Italy

Io provai una cosa simile su un vecchio marantz con doppio tda1540.

Poi inavvertitamente provocai un corto sul saa7000 e quindi lasciami perdere la cosa.

Cmq lo schema è il seguente:

Allegato: no_oversampling.pdf ( 14214bytes )

Allegato: no_oversampling.pdf ( 14214bytes )

Ah il circuito prevedeva anche l'eliminazione del filtro saa7030.

Ciao

Andrea

Poi inavvertitamente provocai un corto sul saa7000 e quindi lasciami perdere la cosa.

Cmq lo schema è il seguente:

Ah il circuito prevedeva anche l'eliminazione del filtro saa7030.

Ciao

Andrea

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Piergiorgio, ti ringrazio moltissimo, come al solito, per la tua competenza, e per come sei pronto a offrirla.

Ti quoto, però, perchè, piuttosto affascinato dalla soluzione PLL ANALOG DEVICE, tuttavia non sono riuscito nemmeno un poco a capire come implementarla nel clock di un cdplayer.

Hai suggerimenti in merito?

La questione dell'uso del flip flop mi rimane più chiara, tuttavia non sono affatto certo che possa funzionare, implemetata come nelle immagini che allego..a valle del clock separato.

Faccio la domanda perchè Drew che ringrazio, non ha portato a termine la modifica, e quindi non c'è un resoconto diretto della efficacia funzionalità.

Saluti

R.R.

Ti quoto, però, perchè, piuttosto affascinato dalla soluzione PLL ANALOG DEVICE, tuttavia non sono riuscito nemmeno un poco a capire come implementarla nel clock di un cdplayer.

Hai suggerimenti in merito?

La questione dell'uso del flip flop mi rimane più chiara, tuttavia non sono affatto certo che possa funzionare, implemetata come nelle immagini che allego..a valle del clock separato.

Faccio la domanda perchè Drew che ringrazio, non ha portato a termine la modifica, e quindi non c'è un resoconto diretto della efficacia funzionalità.

La tecnica Constant Fraction è una bellissima metodologia usata in elettronica nucleare per otetnere temporizzazioni a basso Jitter.Piergiorgio, puoi darci un esempio che mi/ci possa aiutare? (a capire cosa sono i circuiti constant fraction e ALS)

Originariamente inviato da riccardo - 21/03/2006 : 14:39:14

In sintesi si tratta di prendere due segnali (di clock, sinusoidali, impulsivi ..) ritardare uno rispetto all'altro di pochi nanosecondi, scalarlo di un fattore fisso (da cui il nome) e mandare i due segnali così ottenuti agli ingressi di un comparatore ultrafast.

L'impulso che si ottiene in uscita jittera molto meno di quello in ingresso perchè il fronte 'jitteroso' sarà confrontato con una sua replica.

Credo sia più o meno quello che fanno qui:

http://www.lessloss.com/jitter.html

che è una tecnica sostanzialmente diversa dalla più comune (e per certi versi performante) tecnologia a PLL:

http://www.analog.com/en/prod/0%2C2877% ... %2C00.html

Per le diverse famiglie logiche vedi:

http://corsiadistanza.polito.it/corsi/p ... m_log2.pdf

_________

Piergiorgio

Originally posted by plovati - 21/03/2006 : 15:39:37

Saluti

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

-

drews

- new member

- Messaggi: 61

- Iscritto il: 14 nov 2005, 23:56

- Località: Italy

La modifica io personalmente non l'ho più portata a termine, però mi fu passata da un utente di diyaudio e pubblicò i dati anche nel suo sito internet (che ora non trovo più). Comunque molti altri utenti hanno provato questa modifica, quindi credo di poter affermare senza problemi che funziona bene.

In partica fa quello che dici tu Riccardo, al chip principale fornisce la frequenza originale, mentre agli altri a valle fornisce la f/2.

In partica fa quello che dici tu Riccardo, al chip principale fornisce la frequenza originale, mentre agli altri a valle fornisce la f/2.

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Grazie.

Io non ho intenzione di usare il cd senza oversampling ma da quel che vedo dovrebbe andare lo stesso.

R.R.

Io non ho intenzione di usare il cd senza oversampling ma da quel che vedo dovrebbe andare lo stesso.

SalutiLa modifica io personalmente non l'ho più portata a termine, però mi fu passata da un utente di diyaudio e pubblicò i dati anche nel suo sito internet (che ora non trovo più). Comunque molti altri utenti hanno provato questa modifica, quindi credo di poter affermare senza problemi che funziona bene.

In partica fa quello che dici tu Riccardo, al chip principale fornisce la frequenza originale, mentre agli altri a valle fornisce la f/2.

Originally posted by drews - 25/03/2006 : 14:34:39

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

-

mrjam

- starting member

- Messaggi: 357

- Iscritto il: 14 feb 2006, 18:47

- Località: Italy

Il corpo DIL in metallo è connesso al pin gnd, perciò assicura lo stesso grado di schermatura emi per i due oscillatori, benchè non ti indichi nulla dell'aspetto qualitativo di ciò che vi è dentro.XO di Guido Tent.. che costa circa 29 euro+6 di shipping (forse qui si potrebbe aprire un discorso su cosa sia un cristallo risonante privo di jitter, e come si misura la differenza fra un quarzo "jitterizzante" e uno no, premesso il corpo DIL 8 e la tolleranza termica 100PPM di entrambi)

Riguardo la tolleranza termica, la variazione di temperatura che può interessare tale componente è abbastanza limitata e in ogni caso lenta nel tempo, al contrario il jitter è una modulazione della frequenza portante provocata da componenti a frequenza media e alta.

Dunque un buon generatore di clock per circuiti digital audio è quello più preciso in questo ambito, cioè più immune da variazioni veloci della frequenza.

Una variazione lenta della Fs, producendo una altrettanto lenta fluttuazione temporale del momento in cui i 16bit (o 24) vengono convertiti in un valore di tensione (o corrente da convertire), non è avvertibile all'ascolto. Viceversa un jitter veloce produce distorsioni della forma d'onda individuabili nella asprezza della riproduzione.

Guido Tent vende un modulo che dichiara ottimale nelle suddette applicazioni. Se vuoi fidati di lui (e ti assicuro che è un piacere trattare con Guido!), altrimenti usa il modulo che più ti piace.

Purtroppo i mezzi per misurare i circuiti digitali ad alta frequenza, soprattutto nel range di pochi nanosecondi, sono alla portata di pochi.

Un consiglio spassionato a Riccardo e tutti quelli che si divertono col digitale:Piergiorgio, puoi darci un esempio che mi/ci possa aiutare? (a capire cosa sono i circuiti constant fraction e ALS)

Questo luogo oscuro fatto di bit è regolato dagli standard e dalla logica ferrea.

E' necessario un pò di studio (come in tutte le cose!!) prima di metteersi al lavoro! Lo so che è noiosissimo, ma le basi bisogna conoscerle: le famiglie logiche, i livelli logici, il timing, le operazioni logiche, ecc

Basta una leggera distrazione e si presentano i bug!!

A me piace la famiglia VHC, con delay di pochi nS (ma lavora con livelli cmos)

My God!! Ma hai visto bene il datasheet!?! E' un mostro!! Non metto in dubbio le prestazioni super, ma per ottenerle devi:piuttosto affascinato dalla soluzione PLL ANALOG DEVICE, tuttavia non sono riuscito nemmeno un poco a capire come implementarla nel clock di un cdplayer.

Hai suggerimenti in merito?

La questione dell'uso del flip flop mi rimane più chiara, tuttavia non sono affatto certo che possa funzionare, implemetata come nelle immagini che allego..a valle del clock separato.

- interfacciarlo con un microcontrollore (come fai a settarlo per ottenere f/2 ?),

- lavorare con un quadratino smd da 7mm x lato senza pin

- adottare un layout impeccabile con almeno 4 strati, ground plane e power plane

Se hai l'attrezzatura per intraprendere questo progetto, buon lavoro e fammi sapere!

La maggior parte degli audiocostruttori inorridiscono alla sigla smd! Se poi dal SOIC passi al SSOP incominciano i guai, figurati 'sto affarino da lente d'ingrandimento!

Il F-F nella configurazione da te indicata funziona.

Comunque quando non sei sicuro prova una simulazione. Oppure metti sù quattro componenti nella breadboard e fai parlare l'oscilloscopio!!

Ah, ti consiglio di ripulire almeno la linea wordclock (quella che indica al dac a quale canale stereo sono riferiti i dati in ingresso), o meglio tutte le linee dati, portandole all'ingresso D di singoli 74HCT/ALS/(ecc)74 e clockandole con l'uscita del generatore.

Puoi clockare un segnale sottomultiplo del clock senza dividere la Fs, quindi con un circuito abbastanza semplice.

Buon AudioFaidate!

Ciao

Roberto

-

Buon AudioFaidate!

Ciao

Roberto

Buon AudioFaidate!

Ciao

Roberto

-

mrjam

- starting member

- Messaggi: 357

- Iscritto il: 14 feb 2006, 18:47

- Località: Italy

x Riccardo

Ho estrapolato alcuni passaggi di un tread di diyaudio che può esserti di aiuto:

Member:

I was told by a local distributor that the 74HC74 can be employed for reclocking. He said that the Tent XO3 uses a Philips 74HC74N

Tent:

Indeed, it is an HC74

Member:

What do you guys make of this PLL (Phase Locked Loop) synthesizing digital output

Tent:

I wonder why someone uses a PLL in a 1-box solution

Tent:

The clock quality is most important at the DAC. The rest of the players' electronics runs in sync.

Unfortunately the clock usually is generated in the decoder or servo electronics, and transported through some chips to the DAC, adding more jitter.

Depending on the circuitry, the DAC can be clocked directly from a newly placed clock. Usually the TDA1541 runs at half the crystal frequency, reason why my clockboards do have an optional /2 output.

Dall'ultima dichiarazione di Guido puoi concludere che la f/2 è ricavata col circuito F-F da te schematizzato.

Non vi è altra possibilità, infatti il XO3 ha un solo IC: il 74hc74 - F-F tipo D duale, di cui un F-F reclocka il segnale spdif, l'altro divide la frequenza.

Bye - fammi sapere!!

Buon AudioFaidate!

Ciao

Roberto

Ho estrapolato alcuni passaggi di un tread di diyaudio che può esserti di aiuto:

Member:

I was told by a local distributor that the 74HC74 can be employed for reclocking. He said that the Tent XO3 uses a Philips 74HC74N

Tent:

Indeed, it is an HC74

Member:

What do you guys make of this PLL (Phase Locked Loop) synthesizing digital output

Tent:

I wonder why someone uses a PLL in a 1-box solution

Tent:

The clock quality is most important at the DAC. The rest of the players' electronics runs in sync.

Unfortunately the clock usually is generated in the decoder or servo electronics, and transported through some chips to the DAC, adding more jitter.

Depending on the circuitry, the DAC can be clocked directly from a newly placed clock. Usually the TDA1541 runs at half the crystal frequency, reason why my clockboards do have an optional /2 output.

Dall'ultima dichiarazione di Guido puoi concludere che la f/2 è ricavata col circuito F-F da te schematizzato.

Non vi è altra possibilità, infatti il XO3 ha un solo IC: il 74hc74 - F-F tipo D duale, di cui un F-F reclocka il segnale spdif, l'altro divide la frequenza.

Bye - fammi sapere!!

Buon AudioFaidate!

Ciao

Roberto

-

Buon AudioFaidate!

Ciao

Roberto

Buon AudioFaidate!

Ciao

Roberto

- riccardo

- sostenitore

- Messaggi: 4547

- Iscritto il: 08 ott 2005, 02:05

- Località: Italy

Ti ringrazio molto.

Mi permetto di manifestare le mie incertezze, dubbi, solenne ignoranza. Usando un cristallo Xo "à la tent" e messo insieme l'apposito alimentatore dedicato con un Tl7805, l'uscita da un canto va consegnata, con frapposta una r da 47 ohm al pin apposito del SAA, e sempre a valle della R (?) presentata alla porta D del 74HC74, cablato in modo da restituire la F72 al pin 2 del TDA1541 del caso (?).

La stessa cosa usando il clock di Elso, che ha già a bordo sia l'alimentatore sia la R sull'output.

Ammesso che quanto sopra sia lontanamente plausibile, ho due domande: non ho ben capito la questione della "pulizia del WORDCLOCK". Dovendo clockare solo SAA7220P/B e il in F/2 DAC, è necessario, auspicabile frapporre anche all'SAA un 74HC74 mandando il master clock sulla porta D di ques'ultimo?

ehm..

e infine: trattandosi di una modifica "volante" applicata a un vecchio cdp, quale è il sistema di cablatura più "sano" in assoluto?

R.R.

Mi permetto di manifestare le mie incertezze, dubbi, solenne ignoranza. Usando un cristallo Xo "à la tent" e messo insieme l'apposito alimentatore dedicato con un Tl7805, l'uscita da un canto va consegnata, con frapposta una r da 47 ohm al pin apposito del SAA, e sempre a valle della R (?) presentata alla porta D del 74HC74, cablato in modo da restituire la F72 al pin 2 del TDA1541 del caso (?).

La stessa cosa usando il clock di Elso, che ha già a bordo sia l'alimentatore sia la R sull'output.

Ammesso che quanto sopra sia lontanamente plausibile, ho due domande: non ho ben capito la questione della "pulizia del WORDCLOCK". Dovendo clockare solo SAA7220P/B e il in F/2 DAC, è necessario, auspicabile frapporre anche all'SAA un 74HC74 mandando il master clock sulla porta D di ques'ultimo?

ehm..

e infine: trattandosi di una modifica "volante" applicata a un vecchio cdp, quale è il sistema di cablatura più "sano" in assoluto?

Salutix Riccardo

Ho estrapolato alcuni passaggi di un tread di diyaudio che può esserti di aiuto:

Member:

I was told by a local distributor that the 74HC74 can be employed for reclocking. He said that the Tent XO3 uses a Philips 74HC74N

Tent:

Indeed, it is an HC74

Member:

What do you guys make of this PLL (Phase Locked Loop) synthesizing digital output

Tent:

I wonder why someone uses a PLL in a 1-box solution

Tent:

The clock quality is most important at the DAC. The rest of the players' electronics runs in sync.

Unfortunately the clock usually is generated in the decoder or servo electronics, and transported through some chips to the DAC, adding more jitter.

Depending on the circuitry, the DAC can be clocked directly from a newly placed clock. Usually the TDA1541 runs at half the crystal frequency, reason why my clockboards do have an optional /2 output.

Dall'ultima dichiarazione di Guido puoi concludere che la f/2 è ricavata col circuito F-F da te schematizzato.

Non vi è altra possibilità, infatti il XO3 ha un solo IC: il 74hc74 - F-F tipo D duale, di cui un F-F reclocka il segnale spdif, l'altro divide la frequenza.

Bye - fammi sapere!!

Buon AudioFaidate!

Ciao

Roberto

Originally posted by mrjam - 29/03/2006 : 13:05:52

R.R.

Riccardo

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

--------------------------------

"We must believe in free will. We've got no choice.''

--------------------------------

-

mrjam

- starting member

- Messaggi: 357

- Iscritto il: 14 feb 2006, 18:47

- Località: Italy

trattandosi di una modifica "volante" applicata a un vecchio cdp, quale è il sistema di cablatura più "sano" in assoluto?

Intanto fai i test con il doppino twistato, poi valuta il budget.

Usa cablaggi molto corti. Altimenti sei costretto ad aggiungere driver e ricevitori bilanciati (es. RS485)

La R ha lo scopo di dissipare le riflessioni (ricorda che stiamo trattando segnali RF, in cui le tracce e i cavi sono linee di trasmissione) e smorzare leggermente il tempo di salita dell'onda quadra per diminuire le emissioni ad alta frequenza. Il suo posizionamento ideale è prima del pin di arrivo, cioè del SAA.l'uscita da un canto va consegnata, con frapposta una r da 47 ohm al pin apposito del SAA, e sempre a valle della R (?) presentata alla porta D del 74HC74, cablato in modo da restituire la F72 al pin 2 del TDA1541

La linea che si dirige verso il FF (ingresso CLK, non D - al pin D devi riportare l'uscita Q negato) puoi ugualmente terminarla (serie) con una R di basso valore.

Riccardo.. Riccardo..non ho ben capito la questione della "pulizia del WORDCLOCK". Dovendo clockare solo SAA7220P/B e il in F/2 DAC, è necessario, auspicabile frapporre anche all'SAA un 74HC74 mandando il master clock sulla porta D di ques'ultimo?

Il masterclock entra nel pin CLK del FF! I dati entrano nel pin D!

Ancora non mi stai studiando!

In compenso fai studiare me!

La philips chiama il wordclock (cioè clock delle parole digitali.. cioè 16bit (=word) canale destro e successivi 16bit canale sinistro!) in modo leggermente differente: WS, cioè Word Select ( sinonimo

Se vuoi puoi lasciare inalterato il circuito dati e occuparti solo dei clock, ma dato che sei in ballo...

Il segnale WS indica al DAC quando sta ricevendo i 16bit del canale destro e quando del canale sinistro, al termine di ciò avviene la conversione in segnale analogico.

Ti sembra che il jitter in questo segnale sia trascurabile? Mi sembra plausibile che il wordclock abbia il suo ruolo nel trasferirlo ai diffusori.

Puoi reclockare la linea in arrivo al pin 1 del TDA interrompendola e attestandola al pin D del 74hc74 pilotato dal clock a 11.286MHz, dato che il segnale WS è un sottomultiplo del clock non hai il problema di dover frazionare il clock (incrementando il jitter).

Buon AudioFaidate!

Ciao

Roberto

-

Buon AudioFaidate!

Ciao

Roberto

Buon AudioFaidate!

Ciao

Roberto

-

- Argomenti simili

- Risposte

- Visite

- Ultimo messaggio