Inviato: 21 mar 2006, 19:58

Ciao.

pensavo di fare una sistesi tra diverse cose molto popolari che ho trovato

i post di DIY sono questi:http://www.diyaudio.com/forums/showthre ... post734144

e

http://www.diyaudio.com/forums/showthre ... post730231

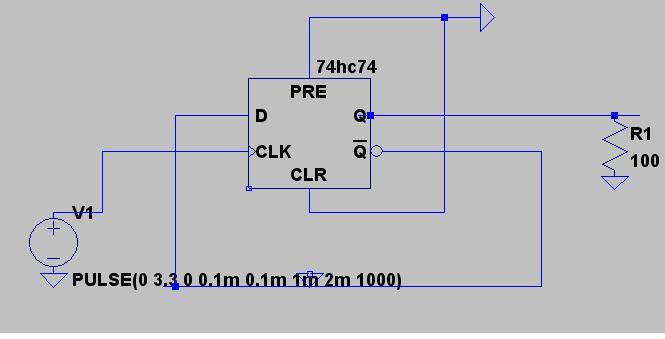

L'IC usato, a valle del clock, per dividere in due la frequenza fornita allo SAA7220p/B dovrebbe essere il philips 74hct74

Pensavo di usare, se riesco a reperirlo, un quarzo della rapid electronic inglese, di tipo DIL8.

Oppure, la prima scelta, l'XO di Guido Tent.. che costa circa 29 euro+6 di shipping (forse qui si potrebbe aprire un discorso su cosa sia un cristallo risonante privo di jitter, e come si misura la differenza fra un quarzo "jitterizzante" e uno no, premesso il corpo DIL 8 e la tolleranza termica 100PPM di entrambi).

Ad ogni buono conto, mentre a valle del clock ci sarebbe l'IC philips, per l'alimentatore avrei pensato a questo:

http://www.tnt-audio.

com/clinica/regulators_noise4_e.html oppure anche la semplicissimo zener della pagina precedente, sempre su TNT. Per ragioni di comodità, potrei prelevare l'alimentazione dal pin IN del regolatore di tensione del +10 V, nel supply del cdp.

Che ne pensate, c'è qualcuno che pensa valga la pena di strutturare questa ideucola, o che ha un parere in merito?

Saluti

R.R.

pensavo di fare una sistesi tra diverse cose molto popolari che ho trovato

i post di DIY sono questi:http://www.diyaudio.com/forums/showthre ... post734144

e

http://www.diyaudio.com/forums/showthre ... post730231

L'IC usato, a valle del clock, per dividere in due la frequenza fornita allo SAA7220p/B dovrebbe essere il philips 74hct74

Pensavo di usare, se riesco a reperirlo, un quarzo della rapid electronic inglese, di tipo DIL8.

Oppure, la prima scelta, l'XO di Guido Tent.. che costa circa 29 euro+6 di shipping (forse qui si potrebbe aprire un discorso su cosa sia un cristallo risonante privo di jitter, e come si misura la differenza fra un quarzo "jitterizzante" e uno no, premesso il corpo DIL 8 e la tolleranza termica 100PPM di entrambi).

Ad ogni buono conto, mentre a valle del clock ci sarebbe l'IC philips, per l'alimentatore avrei pensato a questo:

http://www.tnt-audio.

com/clinica/regulators_noise4_e.html oppure anche la semplicissimo zener della pagina precedente, sempre su TNT. Per ragioni di comodità, potrei prelevare l'alimentazione dal pin IN del regolatore di tensione del +10 V, nel supply del cdp.

Che ne pensate, c'è qualcuno che pensa valga la pena di strutturare questa ideucola, o che ha un parere in merito?

Saluti

R.R.